Figure 5: (Continued).

#### 2.2 With an Active Snubber

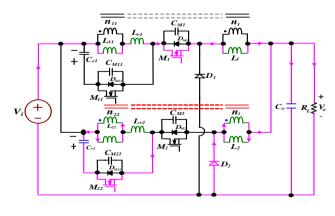

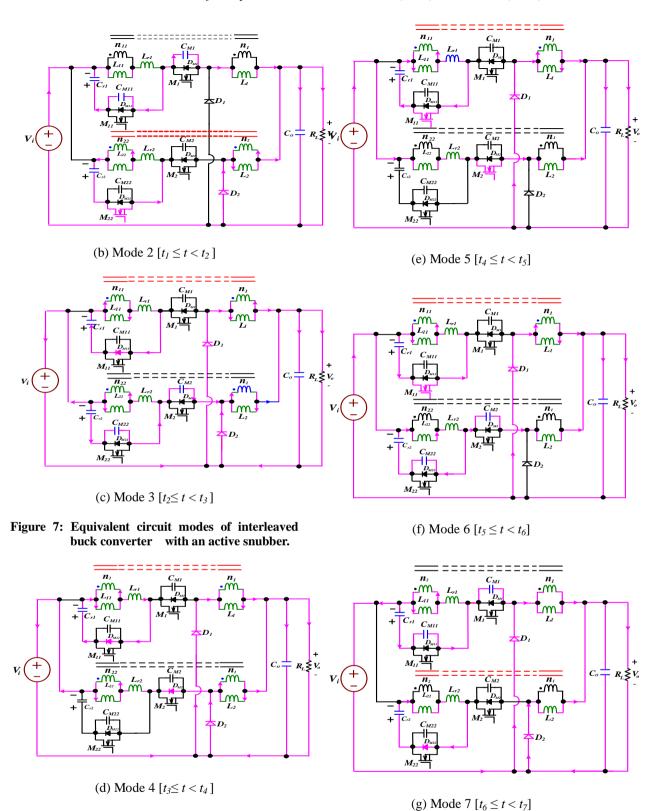

The operation of the interleaved buck converter with an active snubber over one switching cycle can be divided into seven major operating modes. The driving signals, current and voltage waveforms of its key components are shown in Fig. 6. Fig. 7 shows the equivalent circuit modes of the interleaved buck converter with an active snubber over a switching cycle.

## 1). Mode 1 [Fig. 7(a), $t_0 \le t < t_1$ ]:

In this mode, main switch  $M_1$  continuously turned on and auxiliary switch  $M_{22}$  is turned on to create a ZVS condition. The capacitor  $C_{r2}$  begins releasing its stored energy through  $M_{22}$ ,  $L_{r2}$  and  $L_{22}$ . At this interval, coupled inductors  $L_2$  and  $L_{22}$  are discharged continuously to the load.

# 2). Mode 2 [Fig. 7(b), $t_1 \le t < t_2$ ]:

At time  $t_1$ , main switch  $M_I$  is turned off, and auxiliary switch  $M_{II}$  and free-wheeling diode  $D_I$  still stay in the off state. During this interval, main switch  $M_2$  maintains in the off state, while auxiliary  $M_{22}$  as well as free-wheeling diode  $D_2$  still stay in the on-state. In this mode, resonant inductor  $L_{rI}$  releases its energy to stray capacitance  $C_{MI}$  of  $M_I$  and stray capacitance  $C_{MII}$  of  $M_{II}$  with a resonant manner. Stray capacitance  $C_{MII}$  of  $M_{II}$  is charged toward  $(V_i + nV_o)$  while stray capacitance  $C_{MII}$  of  $M_{II}$  is discharged down to zero. To achieve a ZVS feature for switch  $M_{II}$ , the energy stored in resonant inductor  $L_{rI}$  should satisfy the following inequality:

$$0.5 \times [i_{DS1}(t_1)]^2 L_{r1} \ge 0.5 \times [V_{DS11}(t_1)]^2 (C_{M1} // C_{M11}).$$

(13)

Figure 6: Key waveforms of interleaved buck converter with an active snubber.

## 3). Mode 3 [Fig. 7(c), $t_2 \le t < t_3$ ]:

Mode 3 begins when voltage  $V_{DSII}$  of  $M_{II}$  reaches zero at  $t_2$ . Current  $i_{DSII}$  forces the body diode  $D_{MII}$  of  $M_{II}$  conducting and creating a ZVS condition for  $M_{II}$ . The driving signal is applied to switch  $M_{II}$  when its body diode is conducting and achieving a ZVS feature. In this mode, voltage  $V_{DSI}$  of  $M_I$  increases continuously, and then  $V_{DSI}$  of  $M_I$  is clamped to  $V_{in} + V_{CrI}$ . Meanwhile, free-wheeling diode  $D_I$  begins conducting. Coupled Inductors  $L_I$  and  $L_{II}$  are discharged through free-wheeling diode  $D_I$  to the load. The currents of the inductors can be expressed as follows:

$$i_{L1}(t) = \frac{V_o}{nL_1} \times (t - t_2) + i_{L1}(t_2),$$

(14)

and

$$i_{L2}(t) = \frac{V_o}{nL_2} \times (t - t_2) + i_{L2}(t_2).$$

(15)

The energy trapped in the resonant inductor  $L_{rl}$  is recycled to clamp capacitor  $C_{rl}$ . Due to the clamp capacitance of  $C_{rl}$  being large enough, voltage  $V_{Crl}$  will keep constant.

In this mode, when auxiliary switch  $M_{22}$  is turned off at time  $t_3$ , resonant inductor  $L_{r2}$  resonates with  $C_{M2}$  and  $C_{M22}$ . Stray capacitance  $C_{M22}$  of  $M_{22}$  is continuously charged toward  $V_{Cr2}+[n/(1+n)](V_i-V_o)$ , while stray capacitance  $C_{M2}$  of  $M_2$  is discharged down to zero. To achieve a ZVS feature for switch  $M_2$ , the energy trapped in resonant inductor  $L_{r2}$  should satisfy the following inequality:

$$0.5 \times [i_{DS2}(t_2)]^2 L_{r2} \ge 0.5 \times [V_{DS2}(t_2)]^2 (C_{M2} // C_{M22}). \tag{16}$$

# 4). Mode 4 [Fig. 7(d), $t_3 \le t < t_4$ ]:

Mode 4 begins when voltage  $V_{DS2}$  of  $M_2$  drops to zero at  $t_3$ . Current  $i_{DS2}$  forces the body diode  $D_{M2}$  of  $M_2$  conducting and creating a ZVS condition for  $M_2$ . The driving signal is applied to switch  $M_2$  when its body diode is conducting and achieving a ZVS feature.

## 5). Mode 5 [Fig. 7(e), $t_4 \le t < t_5$ ]:

At time  $t_4$ , main switch  $M_2$  is turned on, and auxiliary switch  $M_{22}$  and free-wheeling diode  $D_2$  are in the off states. Current  $i_{L2}$  flows through the path of  $V_i$ - $L_{22}$ - $L_{r2}$ - $M_2$ - $L_2$ - $V_o$ , and inductor current  $i_{L1}$  continuously flows through the path of  $V_o$ - $D_I$ - $L_I$ . Inductor current  $i_{L2}$  linearly increases, and  $i_{L1}$  linearly decreases, which can be expressed as follows:

$$i_{L1}(t) = \frac{V_o}{nL_1} \times (t - t_4) + i_{L2}(t_4), \tag{17}$$

and

$$i_{L2}(t) = \frac{V_i - V_o}{n^2 L_2} \times (t - t_4) + i_{L1}(t_4).$$

(18)

#### 6). Mode 6 [Fig. 7(f), $t_5 \le t < t_6$ ]:

At time  $t_5$ , main switch  $M_2$  is turned off, and auxiliary switch  $M_{22}$  and free-wheeling diode  $D_2$  still stay in the off state. During this interval, main switch  $M_1$  maintains in the off state, while auxiliary  $M_{11}$  as well as free-wheeling diode  $D_1$  still stay in the on states. In this mode, resonant inductor  $L_{r2}$  releases its energy to stray capacitance  $C_{M2}$  of  $M_2$  and stray capacitance  $C_{M22}$  of  $M_{22}$  with a resonant manner. Stray capacitance  $C_{M2}$  is charged toward  $(V_i + nV_o)$ , while stray capacitance  $C_{M22}$  is discharged down to zero. To achieve a ZVS feature for switch  $M_{22}$ , the energy stored in resonant inductor  $L_{r2}$  should satisfy the following inequality:

$$0.5 \times [i_{DS2}(t_5)]^2 L_{r2} \ge 0.5 \times [V_{DS11}(t_5)]^2 (C_{M2} // C_{M22}).$$

(19)

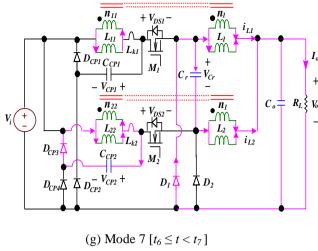

#### 7). Mode 7 [Fig. 7(g), $t_6 \le t < t_7$ ]:

Mode 7 begins when voltage  $V_{DS22}$  of  $M_{22}$  reaches zero at  $t_8$ . Current  $i_{DS22}$  forces the body diode  $D_{M22}$  of  $M_{22}$  conducting and creating a ZVS condition for  $M_{22}$ . The driving signal should be applied to switch  $M_{22}$  when its body diode is conducting and achieving a ZVS feature. In this mode, voltage  $V_{DS2}$  increases continuously, and then  $V_{DS2}$  of  $M_2$  is clamped to  $V_i + V_{cr2}$ . Meanwhile, free-wheeling diode  $D_2$  begins conducting. Coupled inductors  $L_2$  and  $L_{22}$  are discharged through free-wheeling diode  $D_2$  to the load. The currents of the inductors can be expressed as follows:

$$i_{L1}(t) = \frac{V_o}{nL_1} \times (t - t_6) + i_{L1}(t_6),$$

(20)

and

$$i_{L2}(t) = \frac{V_o}{nL_2} \times (t - t_6) + i_{L2}(t_6).$$

(21)

The energy trapped in the resonant inductor  $L_{r2}$  is recycled to clamp capacitor  $C_{r2}$ . Since the clamp capacitor  $C_{r2}$  is large enough, voltage  $V_{cr2}$  will keep constant. In order to achieve a ZVS feature for switch  $M_I$ , the energy stored in resonant inductor  $L_{rI}$  should satisfy the following inequality:

$$0.5 \times [i_{DS1}(t_6)]^2 L_{r1} \ge 0.5 \times [V_{DS1}(t_6)]^2 (C_{M1} // C_{M11}).$$

(22)

When the main switch  $M_I$  starts conducting again at the end of mode 7, the converter operation over one switching cycle is completed.

(a) Mode 1 [ $t_0 \le t < t_1$ ]

Figure 7: (Continued).

# 3. Comparison Between Two Different Snubbers

Soft-switching methods usually add snubbers to the original interleaved buck converter to reduce switching losses. This section presents comparison between two different snubbers of the interleaved buck converters. The features of two different snubbers are described as follows:

### 3.1 Features of the Passive Snubber

In Fig. 1, the interleaved buck converter with the passive snubber has the advantages as follows: 1) It can achieve zero-voltage-transition (ZVT) under turn-off condition. Therefore, the turn-off switching losses of active switches can be substantially reduced. 2) The passive snubber needs only passive components such as diodes and capacitors, which have simple structures and low cost. However, the interleaved buck converter with a passive snubber has disadvantages. For example, the active switches are operated at hard-switching during turn-on transition. As a result, turn-on losses and EMI conditions are significant. Additionally, the passive snubber usually requires many passive components that might increase the complexity of printed circuit board (PCB) layout.

#### 3.2 Features of the Active Snubber

In Fig. 2, the interleaved buck converter with the active snubber has the advantages as follows: 1) It can achieve ZVS feature under turn-on condition and ZVT feature under turn-off condition. Therefore, the switching losses at turn-on transition can be completely removed, and conversion efficiency can be further increased. 2) It can be operated at high frequency, reducing converter size, and EMI. However, the interleaved buck converter with an active snubber has disadvantages. For example, extra active switches and resonant inductor result in complex control.

To objectively judge the merits of two snubbers, the interleaved buck converter with a passive and an active snubber is shown in Table 1.

Table 1: Comparison between the features of two different snubbers in the interleaved buck converters.

|            | with a passive<br>snubber (in Fig.<br>1) | with an active snubber(in Fig. 2) |

|------------|------------------------------------------|-----------------------------------|

| soft-      | <ul><li>hard-switching</li></ul>         | ● ZVS turn-on                     |

| switching  | turn-on                                  | <ul><li>ZVT turn-off</li></ul>    |

| feature of | <ul><li>ZVT turn-off</li></ul>           |                                   |

| active     |                                          |                                   |

| switches   |                                          |                                   |

| componen   | • many                                   | ●less                             |

| t counts   | components                               | components                        |

| power      | • large                                  | • small                           |

| losses     |                                          |                                   |

| control    | • easy                                   | • difficult                       |

| circuit    |                                          |                                   |

# 4. Experimental Results

In order to compare the features between two different snubbers in the interleaved buck converter, a 240W prototype of the interleaved buck converter was built. The specifications are listed again as follows:

input voltage: 150-200 V<sub>dc</sub>,

output voltage: 12 V<sub>dc</sub>,

output current: 20 A, and

switching frequency: 75 kHz.

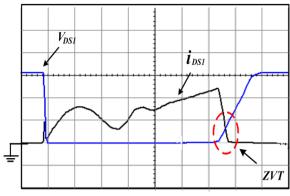

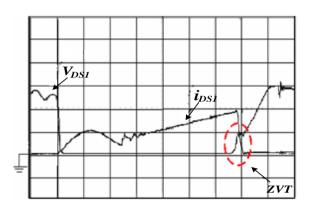

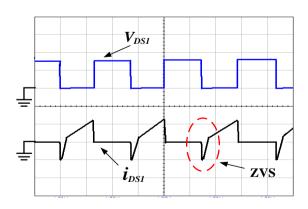

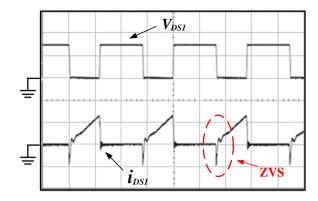

Fig. 8 shows simulated and experimental voltage and current waveforms of the active switches at turn-off transitions for an interleaved buck converter with a passive snubber. From Fig. 8, it can be seen that the active switches have ZVT features. However, it has switching overlap of voltage and current resulting in low switching losses at turn-off transitions. Fig. 9 shows simulated and experimental voltage and current waveforms of the active switches for interleaved buck converter with an active snubber. From Fig. 9, it can be seen that the active switches have ZVS features, and there is not any witching losses at turn-off transitions. Therefore, it has high conversion efficiency and low EMI. Fig. 10 shows efficiency measurements of the interleaved buck converter with a passive snubber and an active snubber. Fig. 10 shows efficiency comparison between two snubbers. It can be seen that the conversion efficiency of an interleaved buck converter with an active snubber can reach 89% under full load condition. This reason is that the active switches have ZVS features, which result in that the switching losses at turn-on transition high efficiency.

( $V_{DS}$ : 100V/div,  $i_{DS}$ : 5A/div, Time: 1 $\mu$ s/div)

(a)

( $V_{DS}$ : 100V/div,  $i_{DS}$ : 5A/div, Time: 1 $\mu$ s/div)

(b)

Figure 8: Voltage and current waveforms of the active switches with a passive snubber:

(a) simulated result, (b) experimental result.

( $V_{DSII}$ : 200 V/div;  $i_{DSII}$ : 10 A/div; Time: 5  $\mu$ s/div)

(a)

( $V_{DSII}$ : 200 V/div;  $i_{DSII}$ : 10 A/div; Time: 5  $\mu$ s/div)

Figure 9: Voltage and current waveforms of the active switches with an active snubber: (a) simulated result, (b) experimental result.

Figure 10: Plots of efficiency versus output current for the interleaved buck converter with a passive and an active snubber under full-load condition.

# 5. Conclusions

In this paper, the comparsion between two different snubbers of an interleaved buck converter has been implemented. The interleaved buck converter with a passive snubber has disadvantages. For example, the active switches are operated at hard-switching during turn-on transition. As a result, turn-on losses and EMI conditions are significant. The interleaved buck converter with an active snubber has the advantages. For example, it can achieve ZVS and ZVT features, resulting in low EMI and high efficiency. For the requirements of high power density, high efficiency and low power losses, the interleaved buck converter with an active snubber is relatively attracted.

# References

- [1]. Ilic, M. and Maksimovic, D.,"Interleaved zero-current-transition buck converter," IEEE Trans. Ind. Appl.,Vol. 43, 2007, pp.1619–1627.

- [2]. M. Xu, J. Zhou, and F. C. Lee, "A Current-Triple DC/DC Converter," IEEE Trans. on Power Electronics, Vol. 19, Issue: 3, 2004, pp. 693 700.

- [3]. Tsai, C.-T.; Shen, C.-L.,"High step-down interleaved buck converter with active-clamp circuits for wind turbines," Energies Vol. 5, 2012, pp. 5150–5170.

- [4]. M. Xu, J. Zhou, and F. C. Lee, "A Current-Triple DC/DC Converter," IEEE Trans. on Power Electronics, Vol. 19, 2004, pp. 693 700.

- [5]. J. A. Abu-Qahouq, H. Mao and I. Batarseh, "New Coupled-Inductors Current-Doubler Topology," Proceedings of Power Electronics Specialists Conference, Vol. 2, 2003, pp. 648-655.

- [6]. A. Pietkiewicz and D. Tollik, "Coupled-Inductor Currenr-Doubler Topology in Phase-Shift Full-Bridge DC-DC Converter," Proceedings of Telecommunications Energy Conference, 1998, pp. 41-48.

- [7]. Tsai-Fu Wu, et al., "Analysis and Implementation of an Improved Current-Doubler Rectifier with Coupled Inductors," IEEE Trans. on Power Electronics, Vol. 23, 2008, pp. 2681-2693.

- [8]. Chen, Y. M., Tseng, S. Y., Tsai, C.T. and Wu, T. F. Interleaved buck converters with a single-capacitor turn-off snubber. IEEE Trans. Aerosp. Electron. Syst. Vol. 40, 2004, pp. 954– 967

- [9]. Shen-Yaur Chen and Jin-Jia Chen, "Study of the Effect and Design Criteria of the Input Filter for Buck Converters with Peak Current-Mode Control Using a Novel System Block Diagram," IEEE Transactions on Industrial Electronics, Vol. 55, 2008, pp. 3159– 3166.

- [10]. N. P. Papanikolaou and E. C. Tatakis, "Active voltage clamp in flyback converters operating in CCM mode under wide load variation," IEEE Trans. Ind. Electron., vol. 51, 2004, pp. 632–640.

- [11]. Chu-Yi Chiang and Chern-Lin Chen, "Zero-Voltage-Switching Control for a PWM Buck Converter under DCM/CCM Boundary," IEEE Transactions on Power Electronics, Vol. 24, 2009, pp. 2120–2126.

- [12]. L. S. Yang, T. J. Liang, H. C. Lee, and J. F. Chen, "Novel high step up dc-dc converter with coupled-inductor and voltage-doubler circuits," IEEE Trans. Ind. Electron., Vol. 58, 2011, pp. 4196–4206.

- [13]. T. F. Wu, Y. S. Lai, J. C. Hung, and Y. M. Chen, "Boost converter with coupled inductors and buck-boost type of active clamp," IEEE Trans. Ind. Electron., Vol. 55, 2008, pp. 154–162.

- [14]. A. Hren, J. Korelic, and M. Milanovic, "RC-RCD clamp circuit for ringing losses reduction in a flyback converter," IEEE Trans. Circuits Syst. II, Vol. 53, 2006, pp. 369–373.

Cheng-Tao Tsai received the B.S. degree in electrical engineering in 1991 from Feng Chia University, Taichung, Taiwan, and the M.S. and Ph.D. degree from the National Chung Cheng University, Chia-Yi, Taiwan, in 2003 and 2008,

respectively. In 2009, he joined the National Chin-Yi University of Technology, Taichung, Taiwan, where he is currently an Associate Professor in the Department of Electrical Engineering. His current research interests include design of switching-mode power supplies, power factor correction technology, and chargers for electric vehicles.

Ying-Che Kuo received the B.S. and M.S. degree in automatic control engineering from Feng Chia University, Taichung, Taiwan, in 1986 and 1988 respectively, and the Ph.D. degree in institute of communications engineering

from the National Chiao Tung University, Hsinchu, Taiwan, in 2005. In 1990, he joined the National Chin-Yi University of Technology, Taichung, Taiwan, where he is currently an Associate Professor in the Department of Electrical Engineering. His current research interests focus on intelligent vehicle, image processing and analysis, and application of embedded system.

Ying-Piao Kuo received the B.S. degree in electrical engineering in 1985 from the National Taiwan University of Science and Technology, Taipei, Taiwan, and the M.S. degree in electrical engineering in 1989

from the National Taiwan University, and Ph.D. degree from the National Taiwan University of Scienceand Technology, Taipei, Taiwan, in 2011, In 1989 he joined the National Chin-Yi University of Technology, Taichung, Taiwan, where he is currently an Associate Professor in the Department of Electrical Engineering. His current research interests include design of switching-mode power supplies, partial discharge and power system stability.

Yung-Chang Luo received the M.S. and Ph.D. degree from the National Taiwan University of Science and Technology, Taipei, Taiwan, in 1991 and 2000, respectively. Currently, he is an Associate Professor at the

Department of Electrical Engineering, National Chin-Yi University of Technology, Taichung, Taiwan. His research interests include speed-sensorless ac motor drives, front-end power factor correction of converter, and design of micro-controller-based motor drive.